中文核心期刊

# 基于 RocketIO 的多路相机数据传输系统的设计

高世杰, 吴志勇

(中国科学院 长春光学精密机械与物理研究所, 长春 130033)

摘要: 数字/模拟图像数据传输一直是测控设备数据通讯中的重点和难点。针对 X I i nx 的 Vi rt ex-PRO 系列 FPGA 内嵌的 Rocket I O 收发器模块,设计了用于测控设备多路图形数据的高速传输系统。该系统充分利用了 FPGA 中集成的 Rocket I O 收发器模块,采用 BREFCLK 差分输入参考时钟,8B/ 10B 编码,预加重处理等技术。实现了多路图像高速、实时、远距离传输。单通道传输速率可以达到 3. 125 Cb/s。关键词: Rocket I Q 多速率吉比特收发器;数字相机接口;逐行倒相制式

中图分类号: TP302.1 文献标识码: A 文章编号:1002-5561(2008)05-0046-03

# The implementation of multiple camera data transmission by RocketlO

GAO Shi-jie, WU Zhi-yong

(Changchun Institute of Optics, Fine Mechanics and Physics, Changchun 130033 China)

Abstrat: In the communication system of observation and control instrument, the high speed data of digital/analog camera transmission is the emphases and the difficulty all the time. Aiming at the RocketlO transceiver module of Xilinx Virtex- PRO FPGA. This paper designs a high-peed transmission system used on data transmission system. This system uses RocketlO module in the chip fully, BREFCLK differential input reference clock, 8B/10B decoder and pre-emphasis technology. Implements one RocketlO transmission at 3.125bps and delivers the data with the characters such as high speed, far distance, and real time.

Key words: RocketIO; MGT; camera link; PAL

## 1 引言

随着光电探测技术和新型武器装备的飞速发展,靶场对测控设备提出了越来越高的要求,新型大面阵,高灵敏度、高帧频、多路、数字/模拟图像传感器正逐步被采用,多探测手段、大数据量数据存储与传输正逐步被应用于测控设备中。然而随着使用的数字相机帧频、像素位宽的提升,图像数据的传输速率已经大大超过1Gb/s,而传统的并行传输,无论是单端并行还是差分并行,发展到今天都已经达到了它们的物理极限,无法为数字相机的数据传输率提供可靠的实现方法,所以经纬仪中图像数据的实时传输需一种更快更可靠的数据传输方式来取代并行传输方式。当前,在系统级互连设计中,高速串行技术迅速取代传统的并行传输技术正成为业界趋势。特别是 Xilinx 公司在其 Virtex-PRO 系列 FPGA 中推出的 RocketlO 收发器硬核,使得

高速串行能够带来更高的性能、更低的成本和更简化 的设计。

针对高速数字相机传输率的要求,下面将详细论述利用光纤为传输介质实时传输图像数据,并且对设计中的关键技术——RocketlO 收发器的使用进行介绍,同时给出系统设计方案、实现方法、实验结果。

### 2 RocketIO 简介

Xilinx 公司的 Virtex II- PRO FPGA 采用具有时钟恢复功能的全双工串行 I/O 收发器, 支持每通道 3.125 Gb/s 的数据速率, 并可利用通道捆绑功能满足各种应用不断增长的数据传输速率的要求。Virtex II- PRO 的收发模块由物理编码子层 (PCS) 和物理介质接入 (PMA)构成。其中物理编码子层提供与 FPGA 逻辑内的数字接口, 内部包括: 循环冗余码校验 CRC、8B/I0B编解码器、先进先出缓冲器 FIFO; 物理介质接入提供与外部媒体的模拟接口。

收稿日期: 2008-01-29。

作者简介: 高世杰(1979-),男,研究实习员, 主要研究方向为数据通讯。

#### 高世杰,等:基于 RocketIO 的多路相机数据传输系统的设计

# 3系统设计方案及其实现

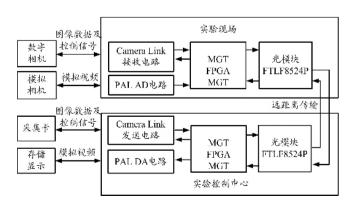

数字相机数据传输系统的功能是满足相机数据远 距离实时传输需要的,系统结构框图如图 1 所示。整个 系统由实验现场和实验控制中心两部分组成,二者通 过光纤远距离连接,对于数字/模拟的图像的采集以及 对传感器的控制都是实时的。

FPGA 是整个通信系统的控制中心,完成对相机 数据的发送以及接收,利用 RocketIO multi-gigabit transceiver(MGT)完成数据的串行化以及解串化。数字 相机数据传输系统主要包括发送、接收两部分。发送部 分的主要功能是,接收相机输出的图像信号、行场信 号,编码后实时发送到光模块中。接收部分完成接收发 送端传送的光信号,恢复出发送端的图像数据,发送给 图像采集卡。模拟部分包括对模拟视频的 AD 和 DA 转换部分, AD 后的数据传输方法同数字图像的类似, 在实验控制中心通过 DA 恢复出模拟视频. 完成存储 和显示的功能。

#### 3.1 接口电路的设计

接口电路主要分为数字图像接口以及模拟接口两 部分。

#### 3.1.1 数字接口部分

在实际工程中,使用的是德国 MIKROTRON 公司 生产的 1302 相机, 该相机采用了 CMOS 传感器, 可以 实现高分辨率高速率的图像采集、当画幅大小设置为 1280(水平) ×1024(垂直)时, 帧频为 100 帧每秒。

考虑到图像输出的方式为 Camera Link 方式,首 先要把四路高速的 LVDS数据信号以及像素时钟信号 转换为 TTL 信号, 以便干在光纤连接器的发送部分接 收图像数据。利用美国国家半导体公司生产的 DS90CR287 以及 DS90CR288 实现 TTL 信号和 LVDS 信号之间的转换。两种芯片的数据带宽相同,高达 297.5MB/s<sub>o</sub>

图 1 系统结构框图

# 3.1.2 模拟接口部分

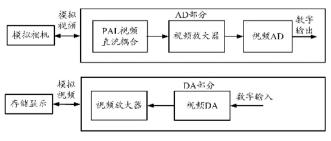

模拟接口部分主要是完成对模拟视频的 AD 以及 DA 功能, 信号的转换质量是设计的关键, 由图 2 所 示。模拟接口主要包括模拟视频直流耦合、视频放大、 视频 AD、视频 DA 几个部分。这里重点提出的是系统 为了提高信号转换质量,选用了 MAX9503 完成对模 拟视频的直流耦合。传统对模拟视频采用的处理方法 是交流耦合,该方法最大的优点就是有保护作用,万一 输出连接器短路至地或电源电压, 电容器可防止晶体 管损坏. 但是这个保护作用是以牺牲信号传输质量为 代价的, 信号的失真较大。MAX9503 应用电路中包括 一个 75 反向端接电阻, 可在视频输出外部短路时限 制短路电流。

#### 3.2 具体实现

系统中选用的 PFGA 型号为 XC2VP20. 该芯片包 含 8 个高速串行收发器。RocketIO 模块的输入时钟由 差分引脚馈人后, 应只经过一级全局缓冲(BUFG) 连接 到时钟树上,再连接到 RocketlO 的参考时钟输入端。 系统的时钟源使用 Xilinx 推荐的高频低抖动的 EG2121CA 差分输出(LVDS) 晶振, 可以提供 53.125~ 700MHz的频率范围和低的抖动 (RMS Period: 3ps; Peak to Peak: 25ps), 可以满足设计中 RocketIO 模块对 参考时钟性能的要求。4个通道 RocketIO 模块采用预 加重,以减小信号高频分量因介质损耗而在收端引起 的信号畸变,从而提高接收数据的质量。

#### 3.3 设计中注意的问题

由于 IP 核是根据 Xilinx 的 FPGA 器件的特点和 结构设计的, 直接用 Xilinx FPGA 底层硬件原语进行 描述, 可充分地将 FPGA 的性能开发出来, 其实现结果 在面积和速度上都能达到令人满意的效果。但是通过 调试 RocketIO IP核, 总结出应当在系统复位、同步状 态机、数据重新对齐3个方面着重考虑,否则系统无法 正常工作, 具体操作参见参考文献[4]。

对于系统的复位,一定要遵循当数字时钟管理 (DCM)的 LOCK 输出端为高时, RocketIO的复位信号

图 2 模拟接口框图

#### 高世杰,等:基于 RocketIO 的多路相机数据传输系统的设计

至少持续两个 USRCLK2 时钟周期的高电平后才能变 成低电平. 从而保证正确地初始化 RocketIO 内部的 FIFO。复位的逻辑代码如下:

module at reset(

USRCLK2 M, DCM LOCKED, RST);

input USRCLK2 M;

input DCM LOCKED; //DCM lock 信号

output RST; //RocketIO 复位信号

wire USRCLK2 M: //DCM 输出的参考时钟

wire DCM LOCKED;

reg RST;

reg [7:0] startup counter; //周期计数器

always @ (posedge USRCLK2\_M)

if (! DCM\_LOCKED)

startup counter <= 8'h0;

else if (startup counter! = 8'h02)

startup\_counter <= startup\_counter+ 1;

always @ (posedge USRCLK2\_M or negedge DCM\_ LOCKED)

if (! DCM\_LOCKED)

RST <= 1'b1:

else //在 DCM LOCKED 为高电平期间

RST <= (startup\_counter! = 8'h02); //RST 保持 两个USRCLK2 M时钟周期

Endmodule//高电平状态

#### 4 布线后仿真实验结果

|L|逻辑设计的初期是对时序的仿真,仿真环境是 ISE8.2 以及 Modelsim SE 6.1b. 仿真原理是将 RocketIOIP核的差分串行发送端(txp, txn)同差分串行接收 端(rxp,rxn)对应管脚分别相连,并行数据通过 MGT 发送端串行化操作后,通过内部连线连接到 MGT 的接 收端,利用在 Modelsim 中的仿真结果,通过对比发送 端和接收端恢复的数据,可以清楚地判断传输的正确 性,同时可以更好地理解 RocketIO 的工作原理。

图 3 中 txdata[31:0]是激励源发送到 MGT 的 32 位 递增并行数据, dataout 是 MGT 接收端恢复出的并行 数据, DV4 是恢复数据的同步时钟信号。其它信号均 为时钟信号以及 MGT 的控制信号。可以看出, 在接收 端恢复的数据同发送端的数据完全相同,只是存在 300ns 内的信号延迟。

图 3 RocketIO 自发自收仿真图

# 5 实测实验结果

由于图像信息是经过 RocketIO IP 核在发送端编 码传输,对应在接收端又做了解码操作,我们有必要对 系统的传输速率、误码率、抗干扰能力、实时性、传输距 离几项重要参数进行测试。实际实验结果如下:

传输速率测试 经过测试, 当系统提供给编解 码芯片的参考时钟为 156.25MHz 时, 通过光纤传输的 数据量达到 3.125Gb/s. 已经达到了所选用 Virtex-PRO 系列 FPGA 的 RocketIO 极限速率。

误码率测试 在发送端传输变化率为 50MHz 的 16 位递增并行数据, 传输时间为 18 小时, 一共传输了 6.48 ×1012 个字节, 在接收端按照递增规律检验, 错误 码为 0 个, 误码低于 10<sup>-12</sup>, 满足系统误码要求。

抗干扰能力测试 在系统检测误码的同时, 开关 电吹风以及电钻设备各50次,传输中没有出现误码。

实时性测试 通过示波器测量发送端以及接收 端信号. 信号延迟低于 300ns。

传输距离测试 由于实验中选用的光纤为波长 为 850nm 的多模光纤, 在没有中继以及放大的情况 下, 传输距离达 300m, 已经满足系统要求。如果想进一 步提高传输距离,可以选择非零色散单模光纤,当然光 模块也应当更换光波长为 1310nm 或者 1550nm 的, 此 时传输距离可以达到 10km。

综合以上实验结果证明:基于 RocketIO 的数字相 机数据传输系统可以远距离、低误码、高实时地传输图 像数据,同时拥有较高地抗干扰能力,完全满足实际工 程的要求。

#### 参考文献:

[1] 唐 炜,史仪凯.Bragg 光纤传感技术应用研究[J].光学精密工程,10(1):

[2] 常春泉, 范 戈.2.5Gb/s 超长距离无中继光纤传输系统的设计与实现 [J].光通信技术, 2005,29(9):34-36.

[3] 卓兴旺.基于 Verilog Hdl 的数字系统应用设计[M].北京: 国防工业出 版社, 2006.1.

[4] RocketIOTM Transceiver User Guide UG024[S].2007.