# 一种基于背照CCD的极紫外成像 电路

申请号:201110449544.2 申请日:2011-12-29

申请(专利权)人 中国科学院长春光学精密机械与物理研究所

地址 130033 吉林省长春市东南湖大路3888号

发明(设计)人 曲洪丰 王晓东 张鑫

主分类号 H04N5/335(2006.01)I

分类号 H04N5/335(2006.01)I H04N5/341(2011.01)I

公开(公告)号 102547154A

公开(公告)日 2012-07-04

专利代理机构 长春菁华专利商标代理事务所 22210

代理人 南小平

www.soopat.com

注:本页蓝色字体部分可点击查询相关专利

## (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 102547154 B (45) 授权公告日 2014.05.28

(21)申请号 201110449544.2

审查员 饶俊

- (22)申请日 2011.12.29

- (73) 专利权人 中国科学院长春光学精密机械与 物理研究所

**地址** 130033 吉林省长春市东南湖大路 3888 号

- (72) 发明人 曲洪丰 王晓东 张鑫

- (74) 专利代理机构 长春菁华专利商标代理事务 所 22210

代理人 南小平

(51) Int. CI.

*H04N 5/335* (2011. 01) *H04N 5/341* (2011. 01)

(56) 对比文件

CN 101146184 A, 2008. 03. 19,

CN 1491028 A, 2004. 04. 21,

权利要求书1页 说明书3页 附图2页

#### (54) 发明名称

一种基于背照 CCD 的极紫外成像电路

#### (57) 摘要

一种基于背照 CCD 的极紫外成像电路,涉及极紫外成像领域,为克服现有基于微通道板的极紫外成像系统体积大、重量大、分辨率低、控制复杂,而且容易出现故障的缺点,本发明提供了一种基于背照 CCD 的极紫外成像电路,该电路包括RS-422 通讯电路、FPGA、驱动模块、背照 CCD、预放电路、视频处理电路、Cameralink 数据传输电路和电源电路;本发明实现了极紫外光信号的光电转换,信号处理和输出;具有体积小、重量轻、分辨率高等优点。

CN 102547154 B

1. 一种基于背照 CCD 的极紫外成像电路,其特征在于,该电路包括 RS-422 通讯电路 (1)、FPGA (2)、驱动模块(3)、背照 CCD (4)、预放电路(5)、视频处理电路(6)、Cameralink 数据传输电路(7)和电源电路(8);

所述 RS-422 通讯电路(1) 向 FPGA(2) 传输外接控制系统的命令;

所述 FPGA (2)接收 RS-422 通讯电路(1)传输的外接控制系统的命令控制整个电路工作、产生背照 CCD (4)工作所需的时序信号输出到驱动模块(3)、对视频处理电路(6)控制及数据处理:

所述驱动模块(3)将时序信号驱动成符合背照 CCD(4)要求幅值的时序信号,驱动背照 CCD(4)正常工作;

所述背照 CCD (4) 将接收的极紫外光信号转换为电信号,输出视频模拟信号到预放电路(5);

所述预放电路(5)将输入的模拟信号进行放大滤波后输出到视频处理电路(6);

所述视频处理电路(6)根据 FPGA(2)的控制时序将模拟信号进行相关双采样和数字量化,将量化后的数字信号传送给 FPGA(2), FPGA(2)对图像进行整合处理;

所述 Camerlink 数据传输电路(7)接收 FPGA(2)整合处理后的图像数据,将图像数据 发送给图像接收系统;

所述电源模块(8)用于对整个电路系统供电。

- 2. 根据权利要求1所述的一种基于背照CCD的极紫外成像电路,其特征在于,所述预放电路(5)包括三极管射随电路和运算放大电路;三极管射随电路进行隔离及阻抗变换,运算放大电路进行放大滤波处理。

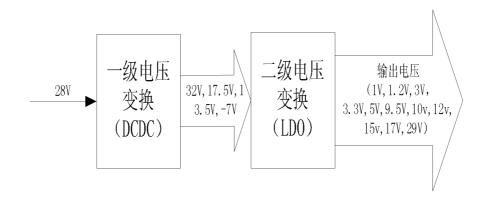

- 3. 根据权利要求1所述的一种基于背照 CCD 的极紫外成像电路,其特征在于,所述电源模块(8) 先使用开关电源芯片进行一级电压转换,然后使用 LDO 芯片进行二次电压变换。

## 一种基于背照 CCD 的极紫外成像电路

#### 技术领域

[0001] 本发明涉及极紫外成像领域,特别涉及一种基于背照 CCD 的极紫外成像电路。

#### 背景技术

[0002] 空间极紫外成像主要在四个极紫外波段 13.0nm、17.1nm、19.5nm 和 30.4nm。目前极紫外成像探测器大多采用基于微通道板的光子计数探测器,由于微通道板需要可以调节的上千伏的高压电源,不仅体积大、重量大、分辨率低、控制复杂,而且容易出现故障。

[0003] 根据器件结构和工艺的不同,CCD分为前照式和背照式。前照式CCD中,光线从电极一面入射,CCD的量子效率比较低,短波响应差,对紫外及其以下波段无响应。而背照式CCD中,光线从无电极的背面入射减少了电极对短波的吸收,具有量子效率高、灵敏度高,短波响应高等优点,并且可通过在背照CCD硅表面制作减反膜,进一步提高短波响应。

[0004] 背照 CCD 这些优点非常适合极紫外成像应用,背照 CCD 可通过非镀膜的工艺达到对极紫外波段很好的响应,相比传统极紫外成像技术,具有体积小、重量轻、分辨率高等优点。

#### 发明内容

[0005] 本发明目的是提供一种可应用于极紫外成像的,基于背照 CCD 的成像电路,克服现有基于微通道板的极紫外成像系统体积大、重量大、分辨率低、控制复杂,而且容易出现故障的缺点。

[0006] 本发明是为克服现有技术的缺点,提出的技术方案:一种基于背照 CCD 的极紫外成像电路,该电路包括 RS-422 通讯电路、FPGA、驱动模块、背照 CCD、预放电路、视频处理电路、Cameralink 数据传输电路和电源电路;

[0007] 所述 RS-422 通讯电路向 FPGA 传输控制系统的命令;

[0008] 所述 FPGA 接收 RS-422 通讯电路传输的控制命令控制整个电路工作、产生背照 CCD工作所需的时序信号输出到驱动模块、对视频处理电路控制及数据处理:

[0009] 所述驱动模块将时序信号驱动成符合背照 CCD 要求幅值的时序信号,驱动背照 CCD 正常工作:

[0010] 所述背照 CCD 将极紫外光信号转换为电信号,输出视频模拟信号到预放电路;

[0011] 所述预放电路将输入的模拟信号进行放大滤波后输出到视频处理电路;

[0012] 所述视频处理电路根据 FPGA 的控制时序将模拟信号进行相关双采样和数字量化,将量化后的数字信号再传送给 FPGA, FPGA 对图像进行整合处理;

[0013] 所述 Camerlink 数据传输电路接收 FPGA 整合处理后的图像数据,将图像数据发送给图像接收系统:

[0014] 所述电源模块用于对整个电路系统供电。

[0015] 本发明有益效果:一种基于背照 CCD 的极紫外成像电路,实现了极紫外光信号的光电转换,信号处理和输出:具有体积小、重量轻、分辨率高等优点。

#### 附图说明

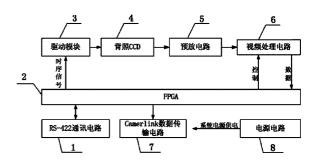

[0016] 图 1 为一种基于背照 CCD 的极紫外成像电路的组成框图;

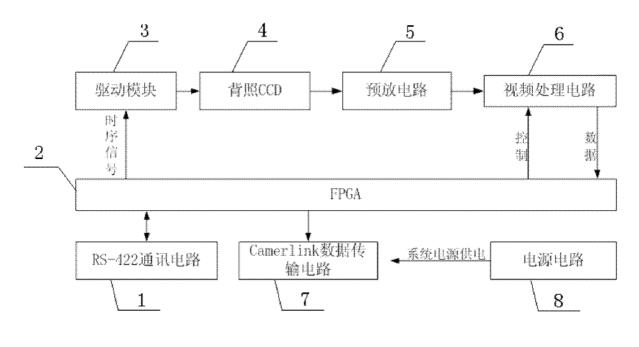

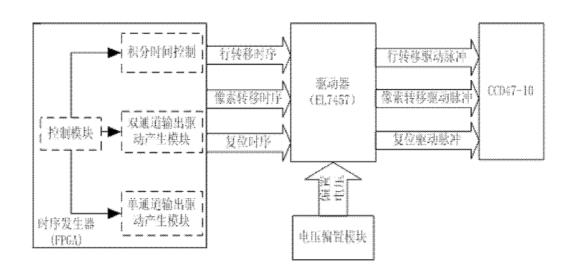

[0017] 图 2 为驱动模块框图;

[0018] 图 3 为电源电路框图。

[0019] 图中,1、RS-422 通讯电路,2、FPGA,3、驱动模块,4、背照 CCD,5、预放电路,6、视频处理电路,7、Cameralink 数据传输电路,8、电源电路。

#### 具体实施方式

[0020] 图 1 是电路的组成框图,包括:RS-422 通讯电路 1、FPGA2、驱动模块 3、背照 CCD4、预放电路 5、视频处理电路 6、Cameralink 数据传输电路 7 和电源电路 8。

[0021] RS-422 通讯电路 1 与所述 FPGA2 连接,用于传输外接控制系统的命令给 FPGA2。

[0022] FPGA2 采用 Xi1inx 公司的 XC3S400-PQ208。FPGA 通过 RS-422 通讯电路 1 接收控制命令控制整个电路工作、产生背照 CCD4 时序信号、对视频处理电路 6 控制、数据整合和输出。FPGA2 的控制模块通过接收控制命令,设置积分时间,以及选择工作模式。积分时间模块通过设置背照 CCD4 的感光积分时间,实现背照 CCD4 感光阵列的电荷积累。在单通道或双通道模式下,时序产生电路产生背照 CCD4 所需的驱动时序,输入驱动芯片 EL7457。由电压偏置电路提供电平参考,使 EL7457 输出的驱动脉冲满足 CCD47-10 驱动脉冲的电平要求,实现对积累电荷的转移输出。

[0023] 如图 2 所示,驱动模块 3 结构,驱动模块 3 分为时序发生器、驱动器以及电压偏置电路三个模块进行设计。其中电压偏置电路由系统的电源模块提供。驱动模块 3 将时序信号驱动成符合背照 CCD4 要求幅值的时序信号,驱动背照 CCD4 正常工作;

[0024] 背照 CCD4 选择英国 E2V 公司生产的全帧式面阵 CCD,型号为 CCD47-10。根据不同的极紫外波段应用,CCD47-10 可以采用不同的镀膜技术。在本发明电路系统应用时,背照 CCD4 接收前端光学系统的极紫外光信号,将极紫外光信号转换为电信号,输出视频模拟信号到预放电路 5:

[0025] 预放电路 5 包括三极管射随电路和运算放大电路,背照 CCD4 输出的模拟信号首先通过预放电路的三极管射随电路进行隔离及阻抗变换,然后通过运算放大电路进行放大滤波后输入给视频处理电路 6。

[0026] 视频信号处理电路 6 包含信号隔直、增益和偏置调节、箝位、相关双采样 (CDS)、A/D 转换及时序发生器等部分。由于分立元件具有电路复杂、调试困难、不利于系统集成等难以克服的缺点,本电路采用专门用于 CCD 输出信号处理的视频处理器。由于背照 CCD4 输出可采用单通道模式或双通道模式输出,因此选用了三通道视频处理器采用 XRD9836,利用其中的两路进行视频处理,减少了电路板面积,提高了集成度。XRD9836 是 EXAR 公司生产的专门用于 CCD 信号采集的集成电路芯片,具有 16 位分辨率 A/D、最大 15MHz 采样频率、相关双采样电路、10 位可编程增益放大器、暗电平校正功能,可通过串行接口对内部寄存器进行配置。视频处理电路 6 根据 FPGA2 的控制时序将模拟信号进行相关双采样和数字量化,将量化后的数字信号传送给 FPGA2,FPGA2 对图像进行整合处理;

[0027] FPGA2 接收视频处理 A/D 量化后的数据进行整合处理后,通过 Cameralink 数据传

输电路 7 将图像数据发送给图像接收系统。接口芯片采用 DS90CR287。根据 CameraLink 协议, CameraLink 数据传输电路数据发送端采用 DS90CR287 芯片,将 28 位数据和 1 位像素时钟信号分别转换成 4 路 LVDS 数据及 1 路 LVDS 时钟信号,连接器选用 3M 公司 Cameralink标准连接器 MDR-26。

[0028] 如图 3 所示,电源电路 8 采用 28V 电源供电,而整个电路总共需要 12 种电压,包括:29V,17V,15V,12V,10V,9.5V,5V,3.3V,2.5V,1.2V,1V,-5V。电源模块框图如附图 3 所示:首先使用开关电源芯片(DC/DC)进行一级电压转换,又由于开关电源芯片(DC/DC)输出电压的纹波和开关噪声较大,不能直接给模拟电路供电,所以使用 LDO 芯片进行二次电压变换,最终获得稳定、低噪声的电压,实现对整个电路系统供电。

图 1

图 2

图 3