FISEVIER

Contents lists available at ScienceDirect

## Materials Science in Semiconductor Processing

journal homepage: www.elsevier.com/locate/mssp

# Investigation of ZrGe Schottky source/drain contacts for Ge p-channel MOSFETs

H. Yang a,b,\*, J. Gao a, H. Nakashima b

- <sup>a</sup> Key Laboratory of Optical System Advanced Manufacturing Technology, Changchun Institute of Optics, Fine Mechanics and Physics, Chinese Academy of Sciences, No. 3888 Dongnanhu Road, Changchun 130033, China

- <sup>b</sup> Art, Science and Technology Center for Cooperative Research, Kyushu University, 6-1 Kasuga-koen, Kasuga, Fukuoka 816-8580, Japan

#### ARTICLE INFO

Available online 18 June 2014

Keywords: Schottky source/drain Zirconium germanide Metal Ge contact Ge MOSFET Hole mobility

#### ABSTRACT

Zirconium germanide (ZrGe) Schottky source/drain (S/D) contacts were fabricated on n-Ge substrates using direct sputter deposition of Zr. The electrical properties of ZrGe/n-Ge contact were investigated and an excellent Schottky characteristic with an electron barrier height of 0.59 eV was obtained, implying an extremely low hole barrier height of 0.07 eV. Using ZrGe as S/D, the operation of Schottky Ge p-channel metal-oxide-semiconductor field-effect transistor (MOSFET) was well demonstrated without any S/D impurity doping. Its good performance indicates that ZrGe is available to S/D in Schottky Ge p-MOSFET.

© 2014 Elsevier Ltd. All rights reserved.

#### 1. Introduction

Mobility enhancement has been regarded as one of the most powerful technology boosters to overcome scaling limits of traditional silicon (Si) metal-oxide-semiconductor field-effect transistor (MOSFET) [1]. Among high mobility materials, Ge is of great interest as a substitute for Si for future high-performance MOSFETs due to its higher intrinsic carrier mobility and relative compatibility with Si processing. To realize high-performance Ge MOSFETs, both source/drain (S/D) engineering and gate-stack engineering are crucial. With the significant progress in gate-stack engineering [2–5], Ge-based MOSFETs with good performance have been demonstrated. However, ultra-shallow highly-doped S/D junction formation remains a technology bottleneck to develop high-performance aggressively scaled Ge MOSFETs because of large diffusion

coefficients and low solubility limits of dopant impurities in Ge [6–9]. In addition, a low-temperature processing is essential for Ge MOSFET fabrication. Therefore, conventional doped S/D technology is difficult to satisfy the requirement of future Ge MOSFETs. As a substitute for doped S/D, metal Schottky S/D is considered as a potential approach to form ultra-shallow S/D junction on Ge substrates because it has low-temperature processing and does not need the complex procedure of implant and activation annealing [1].

To realize ideal metal Schottky S/D, barrier height is a crucial parameter. It should be as low as possible to enhance drive current and suppress leakage current. Theoretical studies have shown that the hole barrier height ( $\Phi_{\rm BP}$ ) of Schottky S/D should be less than 0.1 eV for Schottky p-MOSFETs in order to outperform doped S/D devices [10]. Thanks to the Fermi-level pinning (FLP) near the valence band edge of Ge at the metal/Ge interface [12], metal/Ge contact with low  $\Phi_{\rm BP}$  is formed more easily than that with low electron barrier height ( $\Phi_{\rm BN}$ ), and therefore metal Schottky S/D is more promising for practical application in Ge p-MOSFETs instead of n-MOSFETs. Among various metal germanide, nickel germanide (NiGe)/Ge and platinum

<sup>\*</sup> Corresponding author at: Key Laboratory of Optical System Advanced Manufacturing Technology, Changchun Institute of Optics, Fine Mechanics and Physics, Chinese Academy of Sciences, No. 3888

Dongnanhu Road, Changchun 130033, China. Tel.: +86 431 86708126.

E-mail address: yanghg@ciomp.ac.cn (H. Yang).

germanide (PtGe)/Ge Schottky contacts have been extensively investigated and exhibited great potential for Schottky Ge MOSFETs [12–16]. According to the report by Nishimura et al. [12], zirconium germanide (ZrGe)/Ge formed by electron-beam evaporation might be an alternative contact for Schottky Ge p-MOSFETs because its  $\Phi_{\rm BP}$  is estimated as 0.08 eV, assuming the relation of  $\Phi_{\rm BP}+\Phi_{\rm BN}$  (0.58 eV)=the bandgap ( $E_{\rm g}$ ) of 0.66 eV. Contrarily, in another report by Li et al., its  $\Phi_{\rm BP}$  is as high as 0.53 eV [17], where it is formed by sputter deposition. Therefore, ZrGe/Ge Schottky contact remains to be investigated in detail. Furthermore, the possibility of ZrGe/Ge contact as the Schottky S/D of Ge p-MOSFETs needs to be clarified.

In this study, first we fabricate ZrGe Schottky S/D contact on n-Ge substrates using direct sputter deposition of Zr. Then we evaluate its structural and electrical properties in detail, from which we confirm that an excellent Schottky characteristic with a low  $\phi_{\rm BP}$  of 0.07 eV is obtained. Finally, using ZrGe as S/D we fabricate a Schottky Ge p-MOSFET without any S/D impurity doping and demonstrate its good-performance operation.

#### 2. Experimental details

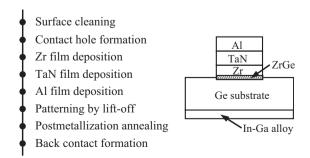

The substrates used in this study are Sb-doped n-type (100)Ge with a resistivity of 0.3  $\Omega$  cm, corresponding to a substrate impurity concentration ( $N_{\text{sub}}$ ) of  $5 \times 10^{15} \text{ cm}^{-3}$ , and In-doped p-type (100)Ge with a resistivity of 0.2  $\Omega$  cm corresponding to a  $N_{\text{sub}}$  of  $2 \times 10^{16}$  cm<sup>-3</sup> [18]. Fig. 1 shows the detailed fabrication processes of ZrGe/Ge contact. After the surface cleaning by HF solution, contact holes with a diameter of 500 µm are formed by photoresist patterning. Then a Zr film with a thickness of 15 nm is deposited directly using radio-frequency (RF) sputtering. The RF power is 10 W and the Ar flow rate is 20 sccm. After that, a 20 nm-thick TaN film is deposited using the same method to prevent the oxidation of Zr films during postmetallization annealing (PMA). Subsequently Al films are deposited using thermal evaporation and the Al/TaN/Zr layers are patterned using a lift-off process. Finally, PMA is carried out at a temperature ( $T_{PMA}$ ) in the range of 300-500 °C in N<sub>2</sub> ambient for 30 min, and In-Ga alloy is rubbed onto back Ge to form an Ohmic contact. The ZrGe/Ge structure is analyzed by transmission electron microscopy (TEM) and Energy Dispersive X-Ray Spectroscopy (EDX). The electrical properties of ZrGe/Ge contact are evaluated by current-voltage measurement. Furthermore, in order to

Fig. 1. Detailed fabrication processes and schematic cross-sectional view of ZrGe/Ge contact.

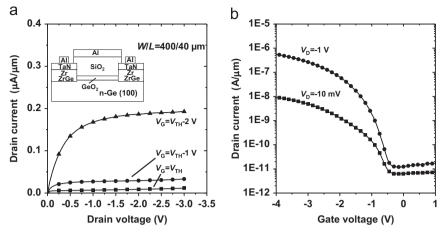

demonstrate the possibility of ZrGe as S/D, a Schottky Ge p-MOSFET is fabricated. A schematic of the MOSFET is reported as the inset of Fig. 6(a) in the next section. The gate-insulator of Ge p-MOSFET is composed of  $GeO_2$  interlayer and  $SiO_2$  layer, which has been described in detail elsewhere [3].

#### 3. Results and discussion

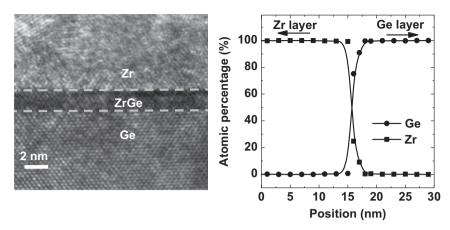

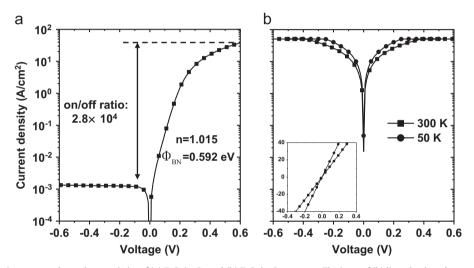

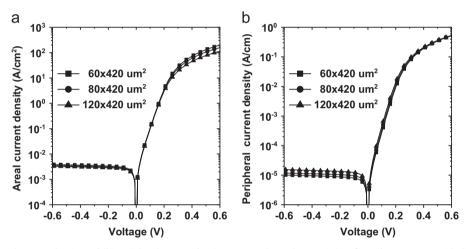

Fig. 2 shows cross-sectional TEM image and EDX results for ZrGe/Ge contact without PMA treatment, from which a ZrGe reaction layer with a thickness of 2 nm between Zr and Ge is found even though there is no PMA. This implies that ZrGe/Ge contact is formed during Zr sputter deposition. The current density versus voltage (J-V) characteristics of ZrGe/n-Ge contact formed at a  $T_{PMA}$ =300 °C are shown in Fig. 3(a). The J-V characteristics of ZrGe/p-Ge contacts are shown in Fig. 3(b), in which the inset linearly plots the corresponding *I*– V characteristics of ZrGe/p-Ge contacts. Clearly ZrGe/n-Ge contact exhibits an excellent rectifying behavior with a low junction leakage-current and a high on/off current ratio of  $2.8 \times 10^4$ , while ZrGe/p-Ge contact in Fig. 3(b) exhibits an excellent Ohmic behavior. Furthermore when the temperature of J-V measurement decreases to 50 K, ZrGe/p-Ge contact still exhibits an excellent Ohmic behavior. By an analysis of the thermionic emission theory [11,12], it is known that generally a metal/semiconductor contact has an Ohmic characteristic regardless of its measured temperature only when its barrier height is very low. Therefore, from Fig. 3(b) we concluded that ZrGe/p-Ge contact had a very low  $\Phi_{BP}$ .

The ideal *J–V* characteristics of ZrGe/n-Ge contact based on the thermionic emission model can be expressed as follows [12]:

$$J = J_{\rm S} e^{qV/nkT} \left[ 1 - e^{-(qV/nkT)} \right] \tag{1}$$

$$J_{S} = A^{*}T^{2}e^{-[q(\Phi_{BN} - \delta\Phi)/kT]}$$

(2)

where  $I_s$  is the saturation current density,  $A^*$  is the Richardson constant (140 for n-Ge), T is the measured temperature, n is the ideality factor, k is the Boltzmann constant, and  $\delta\Phi$  describes the image force lowering of Schottky barrier height.  $\Phi_{BN}$  and n of ZrGe/n-Ge contact can be determined accurately from the slope and interception of log-forward bias ln J versus V plot by assuming  $\delta \Phi = 0$ . Table 1 lists  $\Phi_{\rm BN}$  and n of ZrGe/n-Ge contact with various PMA treatments.  $\Phi_{BN}$  is as high as 0.592 eV and n is close to 1.015 at  $T_{\rm PMA}{=}300~^{\circ}{\rm C}$ . In this study the  $\Phi_{\rm BN}$  of ZrGe/n-Ge contact formed by direct sputter deposition has almost the same value as that of Zr/n-Ge contact reported by Nishimura et al. [12]. They demonstrated that all metal/ n-Ge contacts formed by evaporation deposition exhibited a Schottky characteristic because the Fermi level at metal/ Ge interface strongly pinned near the valence band edge of Ge. Table 1 shows that both  $\Phi_{BN}$  and n have less dependence on  $T_{PMA}$ , which implies that ZrGe/n-Ge contact has an excellent thermal stability in the  $T_{PMA}$  range less than 500 °C. From the high  $\Phi_{\rm BN}$  of 0.59 eV, low  $\Phi_{\rm BP}$  of 0.07 eV is estimated assuming  $\Phi_{\rm BP} + \Phi_{\rm BN} = E_{\rm g}$  (0.66 eV), which is comparable to that of PtGe or NiGe on the n-Ge substrate [13,14]. This electrical performance suggests that

Fig. 2. Cross-sectional TEM image and EDX results for ZrGe/Ge contact without PMA treatment.

Fig. 3. Current density versus voltage characteristics of (a) ZrGe/n-Ge and (b) ZrGe/p-Ge contacts. The inset of (b) linearly plots the corresponding current density versus voltage characteristics of ZrGe/p-Ge contacts.

**Table 1**  $\phi_{\rm BN}$  and n of ZrGe/n-Ge contact with various PMA treatments.

| T <sub>PMA</sub> (°C) | $\Phi_{BN}\left(eV\right)$ | n              |

|-----------------------|----------------------------|----------------|

| 300                   | 0.592                      | 1.015          |

| 500                   | 0.586<br>0.582             | 1.018<br>1.024 |

| 400<br>500            | 0.586<br>0.582             | 1.018<br>1.024 |

ZrGe/n-Ge contact has a great potential as S/D in Schottky p-MOSFET.

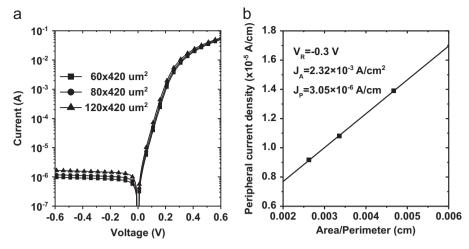

For S/D junction, reverse leakage current ( $I_R$ ) is also an important parameter, which is generally composed of peripheral surface-state generation current and areal current [19,20]. To clarify their contribution to  $I_R$  of ZrGe/n-Ge contact, we prepared the rectangular contacts with the area of  $60 \times 420$ ,  $80 \times 420$  and  $120 \times 420 \, \mu m^2$ . Fig. 4(a) shows the I-V characteristics of ZrGe/n-Ge contact with different size. Generally,  $I_R$  at a reverse bias ( $V_R$ ) can be given by  $I_R = AJ_A + PJ_P$  [19], where A is the contact area, P is the contact perimeter, and  $J_A$  ( $A/cm^2$ ) and  $J_P$  (A/cm) are

areal and peripheral current densities, respectively. Thus,  $J_{\rm A}$  and  $J_{\rm P}$  can be estimated from the slope and interception of the  $I_{\rm R}/P$ –A/P plot. Fig. 4(b) shows the  $I_{\rm R}/P$ –A/P plot at  $V_{\rm R}=-0.3$  V, from which  $J_{\rm A}$  and  $J_{\rm P}$  are estimated as  $2.32\times 10^{-3}$  A/cm² and  $3.05\times 10^{-6}$  A/cm, respectively. As a typical example, the areal current of  $AJ_{\rm A}$  and peripheral current of  $PJ_{\rm P}$  for a junction with a size of  $80\times 420~\mu{\rm m}^2$  were  $7.79\times 10^{-7}$  and  $3.05\times 10^{-7}$  A at  $V_{\rm R}=-0.3$  V, respectively. Thus, the peripheral surface-state generation current and areal current have almost the same contribution to the  $I_{\rm R}$  of  $Z_{\rm R}$ – $C_{\rm R}$ - $C_{\rm R}$

It was reported that peripheral surface-state generation current dominates  $I_R$  in Ge pn junction [19,20]. In this case, the dependence of  $J_A$  on A at  $V_R$  becomes more obvious than that of  $J_P$  on P. Fig. 5(a) and (b) shows the current densities normalized by the area and perimeter of ZrGe/n-Ge contact, respectively. Due to almost the same contribution from peripheral current and areal current in this study, the dependence of  $J_A$  on A at  $V_R$  does not exhibit obvious difference from that of  $J_P$  on P at  $V_R$ . For the forward current in the high-voltage range, it is clearly scaled with P rather

Fig. 4. (a) Current versus voltage characteristics of ZrGe/n-Ge contact with different size; (b) peripheral current density versus area/perimeter ratio.

Fig. 5. (a) Areal current density and (b) peripheral current density versus voltage characteristics of ZrGe/n-Ge contact with different size.

than A in Fig. 5, which is attributed to a series resistance  $(R_{\rm s})$  of the substrate. The main component of  $R_{\rm s}$  is the spreading resistance  $(R_{\rm sp})$  given by  $R_{\rm sp}=\rho_{\rm B}/4r$  for the case of a circle with the radius r, where  $\rho_{\rm B}$  is the substrate resistivity. Thus,  $J_{\rm A}$  is inversely proportional to r while  $J_{\rm P}$  is independent of r. Hence in Fig. 5 the forward current in the high-voltage range is scaled with P rather than with A.

In order to confirm whether ZrGe is available to S/D in Schottky Ge p-MOSFET, we fabricated a p-MOSFET using ZrGe/n-Ge contact. A schematic cross-sectional view of Schottky p-MOSFET is shown in the inset of Fig. 6(a). Its fabrication processes are as follows. After ZrGe/Ge S/D formation, 2.5 nm-thick GeO<sub>2</sub> interlayer and 50 nm-thick  $SiO_2$  layer are fabricated as a gate insulator by plasma oxidation and the subsequent sputtering using an electron cyclotron resonance system, which has been described in detail elsewhere [3]. With the help of the  $GeO_2$  interlayer, the interface-state density between gate insulator and Ge substrate can be reduced to a very low value of approximately  $1 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup> near the midgap. Then post-deposition annealing is performed at 350 °C for 30 min. Gate electrode and S/D contact on ZrGe are formed by

thermal-evaporation Al films and patterned by wet etching. Finally, post-metallization annealing is performed at 400  $^{\circ}\text{C}$  for 30 min.

Fig. 6(a) shows the drain current ( $I_{\rm D}$ ) versus drain voltage ( $V_{\rm D}$ ) characteristics for Ge p-MOSFET with Schottky ZrGe S/D. Excellent operation with good linearity and saturation is observed under accumulation mode, which implies that ZrGe works well as S/D. Fig. 6(b) shows  $I_{\rm D}$  versus gate voltage ( $V_{\rm G}$ ) characteristics. The on/off current ratio is higher than  $10^4$  at  $V_{\rm D}$  = -1 V. This causes the high  $\Phi_{\rm BN}$  of ZrGe/n-Ge contact. From  $I_{\rm D}$ - $V_{\rm G}$  data we extracted field-effect hole mobility ( $\mu_{\rm h}$ ) using the following equation [21]:

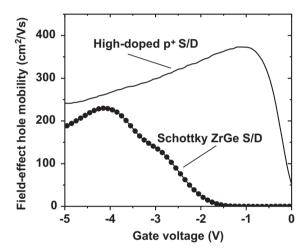

$$\mu_{\rm h} = g_{\rm m}/[(W/L)C_{\rm OX}V_{\rm D}] \tag{3}$$

where  $g_{\rm m}$  is the transconductance, W/L is the channel width/length, and  $C_{\rm OX}$  is the inversion channel capacitance obtained from the gate–channel capacitance. Fig. 7 shows the extracted  $\mu_{\rm h}$  as a function of  $V_{\rm G}$ . As a comparison, the  $\mu_{\rm h}$  of p-MOSFET with high-doped p  $^+$  S/D is also given [3].  $\mu_{\rm h}$  Peak value is as high as 233 cm $^2$  V $^{-1}$  s $^{-1}$  for Schottky MOSFET. This benefits from the extremely low  $\Phi_{\rm BP}$  of ZrGe/

Fig. 6. (a) Drain current versus drain voltage characteristics for Ge p-MOSFET with Schottky ZrGe S/D. The inset is a schematic cross-sectional view of Schottky p-MOSFET; (b) drain current versus gate voltage characteristics for Ge p-MOSFET with Schottky ZrGe S/D.

**Fig. 7.** Extracted field-effect hole mobility as a function of gate voltage for Ge p-MOSFET with Schottky ZrGe S/D. As a comparison, the hole mobility of p-MOSFET with high-doped p<sup>+</sup> S/D is also given.

n-Ge contact for hole injection. However, it is still not comparable to that (376 cm² V<sup>-1</sup> s<sup>-1</sup>) of MOSFET with p<sup>+</sup> S/D and the same gate insulator. We considered that it should come from two  $\mu_h$  limiting factors. One is that ZrGe layer between Zr and Ge shown in Fig. 2 is too thin (2 nm). Another is that ZrGe sheet resistance is close to 60–110  $\Omega$ / $\Box$ , which is higher than NiGe or PtGe as seen from the reports of Gaudet et al. [22]. These two factors are likely to impede hole-injection efficiency from source to inverted channel. In order to realize high-performance Ge p-MOSFET with ZrGe Schottky S/D, further improvement of ZrGe/Ge contact is required.

### 4. Conclusions

In summary, we fabricated the ZrGe/n-Ge contact with excellent Schottky characteristics using direct sputter deposition, and found its  $\Phi_{\rm BN}$  was as high as 0.59 eV, which implies an extremely low hole barrier height of 0.07 eV. Using ZrGe as S/D, we demonstrated the good

operation of Schottky Ge p-MOSFET, and obtained a high  $\mu_h$  of 233 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. Although further improvement of ZrGe/Ge contact is required, this study provides a promising approach to develop Schottky Ge p-MOSFET.

#### Acknowledgments

This work was supported by a Science and Technology Innovation Project (Y3293UM130), a Science and Technology Development Project (Y3453UM130) of Jilin Province, a Science and Technology Innovation Project (Y3CX1SS143) of CIOMP, and a National Natural Science Foundation of China (61306125).

#### References

- [1] (http://www.itrs.net).

- [2] A. Toriumi, C.H. Lee, S.K. Wang, T. Tabata, M. Yoshida, D.D. Zhao, T. Nishimura, K. Kita, K. Nagashio, IEDM Tech. Dig. (2011) 646.

- [3] K. Yamamoto, R. Ueno, T. Yamanaka, K. Hirayama, H. Yang, D. Wang, H. Nakashima, Appl. Phys. Express 4 (2011) 051301.

- [4] M. Caymax, S. Van Elshocht, M. Houssa, A. Delabie, T. Conard, M. Meuris, M.M. Heyns, A. Dimoulas, S. Spiga, M. Fanciulli, J. W. Seo, L.V. Goncharova, Mater. Sci. Eng. B 135 (2006) 256.

- [5] E. Simoen, J. Mitard, G. Hellings, G. Eneman, B. De Jaeger, L. Witters, B. Vincent, R. Loo, A. Delabie, S. Sioncke, M. Caymax, C. Claeys, Mater. Sci. Semicond. Process. 15 (2012) 588.

- [6] C. Claeys, E. Simoen, Germanium-Based Technologies: From Materials to DevicesElsevier, Amsterdam, 2007 (Chapter 3).

- [7] G. Impellizzeri, S. Mirabella, A. Irrera, M.G. Grimaldi, E. Napolitani, J. Appl. Phys. 106 (2009) 013518.

- [8] F. Panciera, P.F. Fazzini, M. Collet, J. Boucher, E. Bedel, F. Cristiano, Appl. Phys. Lett. 97 (2010) 012105.

- [9] G. Impellizzeri, E. Napolitani, S. Boninelli, V. Privitera, T. Clarysse,

W. Vandervorst, F. Priolo, Appl. Phys. Express 5 (2012) 021301.

- [10] Y. Guo, X. An, R. Huang, C. Fan, X. Zhang, Appl. Phys. Lett. 96 (2010) 143502.

- [11] S.M. SZE, K.N.G. Kwok, Physics of Semiconductor DevicesWiley, New York, 2007 (Chapter 3).

- [12] T. Nishimura, K. Kita, A. Toriumi, Appl. Phys. Lett. 91 (2007) 123123.

- [13] S. Zhu, R. Li, S.J. Lee, M.F. Li, A. Du, J. Singh, C. Zhu, A. Chin, D. L. Kwong, IEEE Electron Device Lett. 26 (2005) 81.

- [14] T. Maeda, K. Ikeda, S. Nakaharai, T. Tezuka, N. Sugiyama, Y. Moriyama, S. Takagi, Thin Solid Films 508 (2006) 346.

- [15] M.K. Husain, X.V. Li, C.H. de Groot, Mater. Sci. Semicond. Process. 11 (2008) 305.

- [16] A. Chawanda, K.T. Roro, F.D. Auret, W. Mtangi, C. Nyamhere, J. Nel, L. Leach, Mater. Sci. Semicond. Process. 13 (2010) 371.

- [17] R. Li, H. Yao, S. Lee, D. Chi, M. Yu, G. Lo, D. Kwong, Thin Solid Films 504 (2006) 28.

- [18] S.M. Sze, J.C. Irvin, Solid State Electron. 11 (1968) 599.

[19] K. Yamamoto, T. Yamanaka, R. Ueno, K. Hirayama, H. Yang, D. Wang, H. Nakashima, Thin Solid Films 520 (2012) 3382.

- [20] A. Satta, G. Nicholas, E. Simoen, M. Houssa, A. Dimoulas, B.D. Jaeger, J. V. Steenbergen, M. Meuris, Mater. Sci. Semicond. Process. 9 (2006) 716.

- [21] D. Schroeder, Semiconductor Material and Device Characterization-Wiley, New York, 1998, 501.

- [22] S. Gaudet, C. Detavernier, A.J. Kellock, P. Desjardins, C. Lavoie, J. Vac. Sci. Technol. A 24 (2006) 474.