### 重慶程工大學 学报(自然科学)

Journal of Chongqing University of Technology( Natural Science)

2021 年第 35 卷第 8 期 Vol. 35 No. 8 2021

doi: 10.3969/j.issn.1674-8425(z).2021.08.020

## LUX13HS 的高帧频实时成像系统设计

赵 阳12 孙宏海13 杨 航1 孙海超1 赵 瑜12

(1. 中国科学院长春光学精密机械与物理研究所,长春 130033; 2. 中国科学院大学, 北京 100049; 3. 中科院航空光学成像与测量重点实验室,长春 130033)

摘 要: 为满足国防、科研和工业中高速成像的应用要求,设计了一种基于 CMOS 传感器 LUX13HS 的高速相机。利用现场可编程门阵列(FPGA)作为相机主控元件,驱动 CMOS 图像传感器并接收恢复图像数据,获取平均灰度值和直方图信息并在 DDR4 中进行图像缓存,实现图像预处理和自适应调光,并通过 CameraLink 接口实时传输。系统测试结果表明: 相机在分辨率为 1280 × 720 时,成像帧频为 1 666 fps 实时传输帧频为 555 fps 能长时间稳定工作。自适应调光功能和图像预处理增强了高帧频成像的视觉效果,使相机能适应多种应用场景。

关 键 词: 高速相机; LUX13HS; 现场可编程门阵列; 图像实时处理

中图分类号: TP391.4; TP274 文献标识码: A 文章编号: 1674 - 8425(2021) 08 - 0151 - 09

# Design of High – speed Real – time Camera Acquisition System Based on LUX13HS Sensor

ZHAO  $Yang^{1\,2}$  , SUN  $Honghai^{1\,3}$  , YANG  $Hang^1$  , SUN  $Haichao^1$  , ZHAO  $Yu^{1\,2}$

- (1. Changchun Institute of Optics , Fine Mechanics and Physics , Chinese Academy of Sciences , Changchun 130033 , China; 2. University of Chinese Academy of Sciences , Beijing 100049 , China;

- 3. Key Laboratory of Airborne Optical Imaging and Measurement , Changchun 130033 , China)

**Abstract**: To meet the application demands of high-speed imaging in national defense, research and industry, further enhance the performance of high-speed camera, a high-speed camera acquisition system with CMOS sensor LUX13HS was developed. It is based on the controlling of FPGA, which drives the operation of CMOS sensor, receives and recovers pixels. The camera could process images

基金项目: 国家自然科学基金项目(61401425)

作者简介: 赵阳 男 硕士研究生 主要从事高速成像系统研究 ,E-mail: 18736755223@163. com; 通讯作者 孙宏海 ,男 ,博士 副研究员 ,主要从事先进光电成像技术及高速数字图像实时处理系统研究 ,E-mail: sunhh426@163. com。

本文引用格式: 赵阳 孙宏海 杨航 ,等. LUX13HS 的高帧频实时成像系统设计[J]. 重庆理工大学学报(自然科学) 2021 ,35(8): 151 -159.

Citation format: ZHAO Yang, SUN Honghai, YANG Hang, et al. Design of High-speed Real-time Camera Acquisition System Based on LUX13HS Sensor[J]. Journal of Chongqing University of Technology (Natural Science) 2021, 35(8):151-159.

收稿日期: 2020 - 11 - 18

and exposure automatically by extracting average gray value and histogram from pixels, after putting into DDR4. Eventually, the images were output in real time with CameraLink interface. The camera can work stably with imaging frame frequency up to 1 666 fps and real-time transmission frame rates up to 555 fps, when output 1  $280 \times 720$  pictures. The functions of automatic exposure and image processing embedded in FPGA have big effects on improving the quality of images, which made the camera work in different environment properly.

Key words: high-speed camera; LUX13HS; FPGA; real-time image processing

高帧频成像系统又称高速相机,具有帧频快、数据传输速率大的特点,对许多领域的研究工作具有重要的辅助作用。比如,在国防军事领域可利用高速相机捕捉高速飞行的动态目标运动轨迹<sup>[1-2]</sup>。在科学研究中,高速相机可以记录高速变化的实验过程,提供更高时间分辨率的实验数据<sup>[3-4]</sup>。高帧频成像系统的核心是高速图像传感器。随着固态图像传感器技术的发展,CMOS 图像传感器因具有集成度高、工艺成熟等特点,内部集成了多路 AD 转换,可以实现并行传输,被广泛应用于高速成像系统设计中<sup>[5-6]</sup>。

目前 国内外已经开展了一些 CMOS 传感器 在高分辨率高帧率下的应用研究工作。文献[7] 实现的相机成像帧频为 500 fps ,分辨率为 1 024 × 1 088 ,但最终存入的 SD 卡的储存容量限制了拍 摄时长。文献[8]将获取到的分辨率为2048× 2 048、帧频为 150 fps 的图像存入由 SATA 控制器 组成的磁盘阵列中 能实现长时间拍摄与存储 ,但 是帧频较低,不能即时处理。文献[9-11]采用 CameraLink、以太网等高速数据接口对 CMOS 传感 器捕获到的图像进行实时传输,能解决拍摄时长 受限于相机自身存储容量的问题。但是,为了获 得好的成像效果,获取数据后仍需对图像进行预 处理 整个过程较为繁琐 计算机在处理高速相机 输出的大量数据时也存在一定困难。一些图像预 处理与自动调光的算法,如文献[12]提出的多曝 光融合算法、文献[13-14]提出的区域加权调光 算法和文献[15]提到的指数平滑法能够提升图像 视觉效果和相机工作环境适应能力,但其硬件实 现仅限于较低帧频、低分辨率的相机。

采用 LUXIMA 公司生产的高速 CMOS 传感器

LUX13HS 在 Xilinx Ultrascale 系列 FPGA 上设计了 CMOS 传感器成像控制单元、高帧频图像数据采集单元、缓存单元与传输单元,实现了一个具有自动调光和图像预处理功能的高帧频成像系统。在分辨率为 1 280 × 720 时,成像帧频达到 1 666 fps 实时传输帧频达到 555 fps。

#### 1 系统结构设计

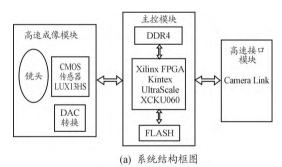

将高帧频成像系统分为高速成像模块、主控模块和高速接口模块3个部分,系统结构和相机整机实物如图1所示。

(b) 系统实物图

图 1 高帧频成像系统结构框图与系统实物图

高速成像模块由相机镜头、CMOS 图像传感器LUX13HS 及其相关电源构成。CMOS 图像传感器将经过镜头成像的光信号转化为电信号,输出给主控模块。主控模块采用 Xilinx 公司的 Kintex Ultrascale 系列现场可编程门阵列 XCU060,相机整

体各芯片的驱动时钟及控制信号均由该模块提供。同时 在主控模块读取图像灰度信息与直方图信息 ,自适应控制曝光时长 将图像在 DDR4 中进行缓存与帧采样 ,进一步预处理。处理后的图像进行并串转换 ,经由高速 CameraLink 接口实时传输。

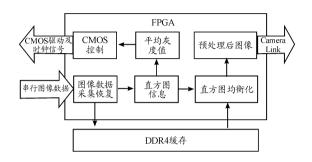

FPGA 顶层设计结构如图 2 所示。

图 2 FPGA 顶层设计结构框图

#### 2 CMOS 图像传感器简介

#### 2.1 LUX13HS 图像传感器性能介绍

LUX13HS 是 LUXIMA 公司开发的高帧频 CMOS 图像传感器芯片。该芯片拥有 100 万像素,

有效像素为 1280 × 864 ,对应 432 个行输出地址 , 支持最大核心时钟为 166 MHz ,满幅下帧率可达到 3 500 fps。在传感器进行开窗时 ,可减小读出的图像数据量 ,提高成像帧频。表 1 列出了该传感器的参数。

LUX13HS 将每个像素的低 2 位与高 8 位分开 从不同输出通道输出,因此可以灵活选择相机输 出图像深度。

#### 2.2 LUX13HS 内部结构

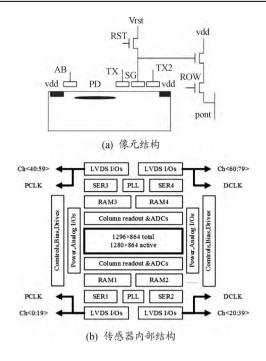

LUX13HS 单个像元由 7 个晶体管构成 ,具有全局快门的功能 ,保证了所有像元能同时启动光积分 ,避免卷帘快门拍摄高速运动物体可能产生的果冻效应。图 3(a) 展示了 LUX13HS 的像元结构 ,PD 是光电探测器 ,SG 是像素内存 ,AB 门上控制信号 'PD\_n' 为低时擦除 PD 上的光电荷 ,为高时允许进行光积分。TX 门上的 "TX\_n'传输脉冲处于低电平使光电荷从 PD 上转移到像素内存 SG上,'TX2\_n'作为第 2 传输脉冲 ,低电平从 SG中移除电荷。RST上 'PRST\_n'低电平会重置 SG ,但传感器会在像素读出时自动重载 ,所以一般置为低电平。

| 像元         | 有效            | 像元                   | 帧频率              | 电压            | 光学       | 饱和满    | 读出               | 量子                   |

|------------|---------------|----------------------|------------------|---------------|----------|--------|------------------|----------------------|

| 结构         | 像素            | 尺寸                   |                  | 响应度           | 格式       | 阱电荷数   | 噪声               | 效率                   |

| 7T         | 1 280*<br>864 | 13.7 μm ×<br>13.7 μm | 3500 Fps@<br>全像素 | 25<br>V/Lux-s | 4/3"     | 30ke – | 15e -            | >45%<br>@550 nm      |

| 转换         | 快门            | 数据                   | 常规时              | 响应非           | 暗信号      | 列 ADC  | 电源               | 供电                   |

| 增益         | 效率            | 输出                   | 钟频率              | 均匀性           | 非均匀性     | 位宽     | 功耗               | 电源                   |

| 40<br>μV/e | 99%           | 80LVDS<br>10 bit     | 133 MHz          | 1.5% rms      | 0.5% rms | 10b    | 2W@<br>3 500 Fps | 3.3 V 模拟<br>1.8 V 数字 |

表 1 LUX13HS 图像传感器参数

LUX13HS 内部框图如图 3(b) 所示 传感器拥有 80 个差分输出端口 感光区域可以分成 4 个象限。结构上分为顶部读出模块和底部读出模块两个部分 ,每个读出模块包括采样电路、放大器和带有可读逐次逼近寄存器的 ADCs(模数转换器) 寄存器 具有相互独立的控制信号和时钟 ,使得顶部读出模块和底部读出模块可以同步输出不同地址数据。传感器外部 I/O、内部结构、电源资源左右

对称,保证传感器的高帧频特性。

LUX13HS 传感器提供 reduced 工作方式。在这种工作状态下,传感器内部核心时钟变为正常模式的 1/2,输出端口减少为 40 个,当可使用的 I/0接口具有数量限制时可使用该模式。由于传感器核心时钟降低,不再受最高时钟限制,因此该模式帧频高于正常模式帧频的 1/2,可以达到 2 500 fps。

图 3 LUX13HS 结构图

#### 3 系统各功能模块实现

#### 3.1 高速成像模块

CMOS 图像传感器通过光电效应的原理 将感受到的光信号转化为光电荷 ,光电荷通过内部的 A/D 变化为数字信号输出。由 FPGA 对 LUX13HS 图像传感器提供驱动时序 ,并进行数据接收采集。

#### 3.1.1 CMOS 图像传感器控制

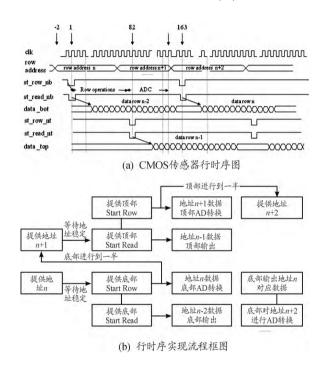

LUX13HS 图像传感器拥有 Start Row 控制信号 "st\_row\_n")和 Start Read 控制信号 "st\_read\_n")。Start Row 信号读取一个地址对应的光电荷并进行模数转换 Start Read 信号控制数据输出。为了实现最大的数据吞吐 LUX13HS 顶部和底部各有 1个 Start Row 和 Start Read 控制信号 ,可以实现顶部与底部同时对不同地址进行 AD 转换和读出。

LUX13HS 控制行时序如图 4(a) 所示,传感器使用二进制编码进行寻址,每个地址对应两行连续的像素数据,在  $1~280 \times 720$  分辨率下共使用 360 个地址。给定了一个行地址 n 后 需要 6 个时钟等待地址稳定,之后发送 Start Row 信号通过传感器底部读出模块进行模数转换。底部 AD 转换进行到一半时,更改地址为 n+1 地址稳定后提供

顶部 Start Row 信号 ,可以利用顶部读出模块对地址 n+1 对应的行进行 AD 采集。AD 采样结束后发送 Start Read 脉冲使传感器输出数据 ,实现了顶部读出模块和底部读出模块同时工作 ,DA 采集和数据输出同步进行 ,保证 CMOS 传感器高帧频特性。FPGA 实现行时序流程如图 4(b) 所示。

图 4 LUX13HS 图像传感器行时序图 及其实现流程框图

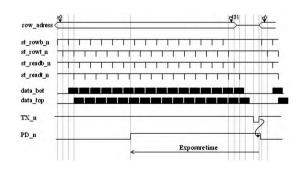

图 5 展示了 CMOS 传感器帧时序 输出每帧 图像数据之前将 PD\_n 拉高 維持时间长短决定了 CMOS 传感器曝光时长。曝光结束之前 TX\_n 信号 的低电平脉冲可以传送出采集到的光电荷 之后再通过行时序控制每行地址对应像素数据输出。

图 5 LUX13HS 行时序图

LUX13HS 工作在 Reduced 模式下,主时钟 100 MHz,每个时钟输出 4 个像素数据,顶部输出模块和底部输出模块同步输出两个地址对应的 4 行数据。输出完整一行图像需要 1 280 ÷ 4 = 320 个周期,完整输出一帧 720 行需要 320 × 720 ÷ 4 = 57 600 个时钟周期。为了给光电荷从像元转出以及清除上一次光积分的剩余电荷提供充足的时

间 设置每帧 60~000 个时钟周期进行输出。由此,可以计算出 LUX13HS 传感器成像帧频为  $100M \div 60~000 \approx 1~666~fps$ 。

#### 3.1.2 CMOS 传感器偏置电压供应

为了使 LUX13HS 传感器正常工作,需要提供 17 种偏置电压,如表 2 所示。

| 表 2 CM | IOS 传 | 感器 | 偏置 | 电压 |

|--------|-------|----|----|----|

|--------|-------|----|----|----|

V

| <br>名称   | 说明            | 典型值  | 名称    | 说明          | 典型值  |

|----------|---------------|------|-------|-------------|------|

| VADL     | 数模转换器低参考电压    | 0.00 | VRSTH | 像素复位高电压     | 3.30 |

| VAD4     | 第二数模转换器偏置电压   | 0.25 | VTXL  | 像素转移低电压     | 0.00 |

| VLNC     | 比较器电流控制电压     | 0.90 | VOFF  | 数模转换器偏置电压   | 0.50 |

| VLNA     | 列放大器电流控制电压    | 0.95 | VPIX  | 像素复位电压      | 1.80 |

| VLN      | 像素缓冲电流控制电压    | 0.50 | VREF  | 放大器参考电压     | 1.20 |

| VCAS     | 内部产生 AMP 级联电压 | 1.40 | VTXH  | 像素转移高电压     | 3.30 |

| VADH     | 数模转换器高参考电压    | 1.00 | VMUX1 | VLNs 否决改变电压 | 1.00 |

| VABL_TST | 像素 AB 测试电压    | 0.20 | VMUX2 | VLNs 否决改变电压 | 1.00 |

| VTX2L    | 像素二级转移低电压     | 0.70 |       |             |      |

其中 VADL 和 VTXL 可以接地实现,配置 CMOS 传感器寄存器内部产生 VLN、VLNA 和 VLNC 电压。剩余偏置电压通过 Analog 公司生产的多通道 12 位 DAC 芯片 AD5674R 提供,该芯片通过 SPI 协议进行配置,具有高相对精度、低增益误差和低温漂特点,满足 CMOS 传感器对偏置电压的要求。为了增强 DAC 输出的带载能力,降低输出电阻并实现隔离,在 DAC 输出和偏置电压输入之间加入跟随器。

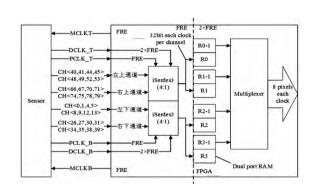

#### 3.1.3 CMOS 图像传感器数据采集

图 6 是 FPGA 数据采集与图像信号恢复结构, CH 使用传感器数据输出通道,FRE 代表时钟频率,虚线将图示结构分为 CMOS 传感器时钟域与 FPGA 内部时钟域。由 FPGA 为传感器提供 MCLKB 和 MCLKT 时钟信号与驱动信号,CMOS 传 感器输出串行数据与伴随数据的时钟 PCLK 和 DCLK,通过 FPGA 内部 iSerdes3 进行并串转换。

图 6 FPGA 数据采集与图像信号恢复结构框图

LUX13HS 同时输出 4 行数据,每行数据单独存入 1 个双口 Ram,利用乒乓缓存实现 Ram 的存取相互独立并同时进行。最后,多路选择器选择 4 行按先后次序输出,恢复出图像信号。

#### 3.2 主控模块

整个系统采用 XCU060 作为主控芯片,可依据不同的需求进行编程,实现不同的硬件功能,最小化电路板的空间与整个系统的体积。在主控模

块实现的功能有: 各芯片工作寄存器参数配置、逻辑时序控制、高速图像数据采集与解码、直方图与灰度信息提取、图像预处理与传输。由于图像按行进行读取和传输,还需通过外部储存器作为成像暂存器。系统引入 DDR4 芯片,总位宽 64 bit,总容量为 2 GB 数据传输速率最高为 3 200 MT/s,可满足系统实时传输性能要求。

#### 3.2.1 图像数据跨时钟域处理

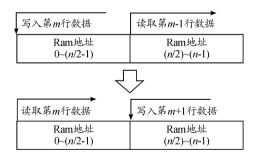

在进行图像数据采集、DDR4 存取与打包发送时,会遇到前后模块位宽、时钟不一致的情况。例如 在图像从 DDR4 读取打包发送的过程中,采用Vivado 上 MIG DDR4 IP 核实现对 DDR4 的控制。IP 核数据时钟为 300 MHz .位宽为 512 bit .但 CameraLink Full 模式数据时钟为 80 MHz .位宽为 64 bit 必须对数据进行跨时钟域处理。一般采用先存再取的方式时,存取等待时间会加长行场之间的开销时间,降低相机帧频。所以采用乒乓缓存,同时对双口 Ram 进行读写操作,示意图如图 7, n 为一个偶数 表示 Ram 的地址总数。

在初始化时,写时钟将一行图像数据存入 Ram 地址  $0 \sim (n/2-1)$  中,同时读取 $(n/2) \sim (n-1)$  地址中的数据,实现读写同步进行。在读写均完成之后,交换读写地址,从地址  $0 \sim (n/2-1)$  中读取刚写入的一行数据,并将新的一行数据写入地址 $(n/2) \sim (n-1)$  中。

图 7 Ram 读写实现乒乓缓存过程示意图

#### 3.2.2 基于 FPGA 的图像直方图获取

在获取图像直方图信息与平均灰度信息时,如何做到通过 FPGA 实时提取一帧图像数据信息并进行处理传输是设计的重点。由于 FPGA 内部储存空间有限,因此通过 DDR4 对已经提取过的

数据进行缓存 获取到整个帧的像素统计数据后, 再从 DDR4 中提取对应图像进一步处理传输。

FPGA 通过译码器和计数器组成的结构获取 图像直方图数据。译码器读取一个像素值,并在 对应灰度级输出口输出1个高电平脉冲,计数器 在检测到高电平脉冲后加1。本设计中,FPGA将 恢复出的图像数据按行传输,多个像素同时输出 时,有可能会出现多个具有相同灰度值的像素。 这种情况下 利用1个译码器只能输出1个计数 脉冲 会造成计数器计数错误 根据 DDR4 输入数 据位宽设置译码器和计数器数量会耗费大量 FP-GA 逻辑资源 ,若减少同时输出的像素个数 ,则为 了保证实时传输需要提升像素频率。综合考虑性 能要求,设定每时钟向译码器传输8个像素,像素 时钟为 200 MHz 图 6 将 8 个像素输入 1 个直方图 统计模块 统计完一帧数据后再利用加法器获取 完整直方图信息进行储存。对于 256 灰度级、 1 280×720 的图像 ,共 921 600 个像素。FPGA需 要产生8×256=2048个20位计数器,以进行直 方图信息统计。

为了保证在一帧图像进行直方图均衡化同时 获取下一帧图片的信息,采用双口 Ram 实现乒乓 缓存,以灰度值作为 Ram 地址进行存取。

#### 3.2.3 直方图均衡化处理

直方图均衡化是通过累计直方图将图像原直方图变化成均匀分布的形式,可增加像素灰度动态范围与图像对比度。直方图均衡化的变换函数T(r) 如式(1) 所示。其中r 代表归一化后的图像原灰度值s 代表进行直方图均衡化以后的图像灰度值 $p_r(r)$  代表随机灰度值r 的概率密度T(r) 即原图像直方图的累积分布函数。

在数字图像处理中,像素值是离散化的,因此用各个灰度值出现频率代替概率,变换函数  $T(r_k)$  的离散形式可以表示为式(2)。 其中 k 表示归一化前的灰度值  $r_k$  代表归一化后的灰度级  $s_k$  表示变换后的灰度值 N 表示一幅图像的总像素个数, $n_i$  代表灰度级为 i 对应的像素个数。

$$s = T(r) = \int_0^T p_r(r) dr \qquad (1)$$

$$s_k = T(r_k) = \sum_{i=0}^k p_r(r_i) = \sum_{i=0}^k \frac{n_i}{N}$$

(2)

FPGA 实现乘除法以及浮点数运算较为困难,因此直接将归一化的像素值转化为 256 灰度级图像。原灰度值 k 与直方图均衡化以后的灰度值 t 对应关系见式( 3) 。一些设计通过乘法器和除法器 IP 核实现式( 3) 的计算 [16] ,但这样会增加帧开销时间与 FPGA 的逻辑资源占用。本设计采用移位运算,乘以 255 可以将累计直方图按位左移  $\log_2 255 \approx 8$  位实现,除以图片总像素个数 921 600 可以通过将累计直方图右移  $\log_2 921$  600  $\approx$  20 位实现。

$$t = T(k) = \sum_{i=0}^{k} \frac{n_i \times 255}{921\ 600}$$

(3)

利用 Matlab 将此种运算方法与浮点运算做比较 得到累计直方图与均衡化后灰度值对应关系如图 8(a) 所示。可以看出 在灰度级较高的位置误差会明显增大 这是因为随着数据位数增加 较高位取值对数据值大小的影响增加。但是误差与累计直方图成正比 经过拟合得到误差函数为:

$$e(k) = 0.00003 \times \sum_{i=0}^{k} n_i$$

(4)

乘  $0.000\,03\,$  通过将累计直方图右移  $\log_20.000\,03\,$  ≈  $15\,$  位进行计算。最终 均衡化后的灰度值由累计直方图右移  $12\,$  位加右移  $15\,$  位得到。进行误差补偿后 移位运算得到的映射曲线与浮点运算映射曲线相重合,误差接近于  $0\,$  如图  $8(\,b)\,$  所示。此种运算方式非常符合  $FPGA\,$  的运算特性,也保证了计算的精度。

#### 3.2.4 自动调光算法

CMOS 传感器获取的图像亮度取决于像元内部光电荷积累的数量,而光电荷积累多少和当前曝光量之间有如下关系:

$$Q = \eta q \Delta n_{eo} A T_c \tag{5}$$

其中:  $\eta$  代表 CMOS 器件量子效率; q 为电子电荷量;  $\Delta n_{eo}$ 是入射光的光子流速率; A 是器件的感光面积;  $T_e$  为积分时间。可以得出,在已经选取好CMOS 器件、并且光照条件固定的情况下,光电荷积累数量与积分时长  $T_e$  成正比。因此,更改积分时间长短是一种较为灵活的调光方法。

图 8 累计直方图与均衡化后灰度值映射关系曲线

若已知前一帧图像平均灰度值  $R_p$  与曝光时间  $T_p$  ,为了达到目标灰度值  $R_i$  ,可以通过式(6) 计算后一帧需设置曝光时间  $T_i$ 。

$$\frac{R_p}{T_n} = \frac{R_i}{T_i} \tag{6}$$

在设定目标平均灰度值时,应注意不能设置为固定值,因为系统无法保证获取到图像灰度值刚好为某一确定值,否则可能会导致超调震荡。只能将目标灰度值选在一个范围区间内,当帧平均灰度值落在取值区间内时,即调整完成。经测试区间取  $[R_i-15,R_i+15]$  时可以获得较好的成像效果。

LUX13HS 提供电子全局快门 通过信号  $AB_n$  高电平持续时钟周期数控制曝光时长。在上一帧 图片输出时控制  $AB_n$  在一定范围内成高电平 ,可以开始曝光 曝光时间为  $N \times T_H$  , $T_H$  为 1 个周期时间 N 为持续周期数。因此 N 越大 ,CMOS 曝光时间越长,且由于 N 可以选择为小于帧持续周期数的任意 1 个正整数,可以实现无极调光。当前获取图像平均灰度值落在区间右侧时,逐渐减小 N 的取值 缩短曝光时长。若当前图像平均灰度值

落在区间左侧 则增大 N 的取值 提高曝光时长。 3.2.5 帧采样

LUX13HS 工作在 100 MHz 的时钟下 ,成像帧 频达到 1 666 fps。由于传输接口传输速率限制 ,为了保证实时传输的稳定性 ,必须进行帧采样。在 FPGA 从 CMOS 传感器输出数据并恢复出行场信号后 ,将数据缓存入 DDR4 ,最多可存入 2 GB/(1 280  $\times$ 720  $\times$ 8 bit)  $\approx$ 2 330 帧。每存入 3 帧 ,读写仲裁模块允许读取写入的第 1 帧 ,进行 3:1 采样 ,存满 2 330 帧后回到初始地址 继续下个循环 ,保证图像连续性。同时 ,在获取图像直方图时 ,也只获取连续写入 DDR4 的 3 帧中第 1 帧图像直方图 ,用于从 DDR4 读取时进行直方图均衡化。

#### 3.3 高速接口模块

高速传输接口传输带宽保证了高速相机采集 图像数据的实时传输速率。目前常用的工业相机 接口及其性能见表 3。系统在进行对比之后,选择 CameraLink 接口 Full 模式进行高速图像传输。

表3 主流接口性能比较

| 接口               | 最大速率/<br>Gbps     | 传输距<br>离/m | 复杂<br>度 | 实时<br>触发 |

|------------------|-------------------|------------|---------|----------|

| CoaXPress        | $N \times 6.25$   | 100        | 中       | 有        |

| CameraLink HS    | $2N \times 3.125$ | 15         | 中       | 无        |

| CameraLink       | 5.5               | 10         | 低       | 有        |

| USB3.0           | 5                 | 3          | 中       | 无        |

| GigE Vision 1. x | 2                 | 100        | 高       | 无        |

CameraLink 接口是一种抗干扰能力强、传输带宽较高、应用非常广泛的接口,一般相机设计中,采用专用 DS90CR287/DS90CR288A 将 FPGA 输出的 28 位并行数据转化为 4 路串行差分信号传输<sup>[17-18]</sup>。若采用此种设计,Full 模式需要 3 个并串转换芯片 极大增加了相机的体积,因此本系统采用 FPGA 的 oSerdes3 原语直接实现并串转换。这种方式克服了并串转换芯片带宽对接口最大传输速率的限制,选择合适的图像采集装置可以大幅提升数据传输速率<sup>[19]</sup>。CameraLink 数据传输速率为80 MHz,每行和每帧的时间间隔为40 个时钟周期,每个时钟传输8 个像素。因此,对于

$1280 \times 720$  的图像,能够支持最大实时传输帧率达到  $555~\mathrm{fps}$ 。

#### 3.4 相机控制

系统使用 CameraLink 接口的 2 个控制信号 CC1 和 CC2 ,用于设置相机是否启用直方图均衡 化功能和自动调光功能。除此之外,CameraLink 接口提供了两个差分对信号,用于主机端与相机进行串行通讯。SerTFG 是相机发送至图像采集卡的串行信号,SerTC 用于相机接收主机发送的串行数据。串行数据一帧为 10 位,包含 1 个起始位和 1 个停止位 利用上位机可以灵活配置相机系统自动调光目标灰度值,FPGA 根据给定灰度值自动设置调光范围。

#### 4 系统测试

采用 CameraLink 图像采集卡采集相机输出的 图像数据。通过上位机显示并实现串行通讯与控 制 在 FPGA 内部利用 1 个计数器计算 LUX13HS 传感器的成像帧频。

利用 ILA 调试核抓取计数器信号,观察到 CMOS 传感器每秒获取了 1 666 帧图像,上位机显示实时传输帧频约为 555 fps。图 9 展示了未启用相机自动调光与直方图均衡功能和启用后的图像。可以看出,在过曝时启用自动调光能够有效降低图像亮度。在图像暗部细节不清晰时,启用直方图均衡化可以显著增强图像对比度。

(a) 未开启自动调光情况下, (b) 设定自动

SAME UND

(b) 设定自动曝光目标灰度值 为120,过曝消失

图像过曝

(c) 设定自动曝光目标灰度值 为90,图像整体偏暗

(d) 开启直方图均衡化, 暗部 细节变得可以分辨

图 9 相机测试图像

经测试发现:本设计实现的高帧频成像系统能够满足许多基本的工业成像应用需求;自适应调光和预处理功能在场景亮度均匀情况下,能使成像图像呈现较好的显示效果;实时传输功能在一定程度上解决了传统高速相机拍摄时间短、后续处理工序复杂的问题。但是,相机实时传输帧频还有提升空间,缓存入 DDR4 的所有图像由于接口带宽限制无法全部传出;采用平均灰度值作为自动调光的反馈信号,在某些背景与目标亮度差异较大的情况下可能无法获得很好的调光效果。

#### 5 结论

采用高速 CMOS 传感器 LUX13HS,提出了一种具有自动调光、实时预处理功能的高帧频成像系统设计方案。通过 FPGA 实现 sensor 控制、数据读写、传输、乒乓缓存、帧采样,保证了成像帧率高达 1 666 实时传输帧率达到 555 fps。在打开自动调光功能,设置合理参数,并启用直方图均衡化以后,获得了良好的图像效果,为后续研究提供了可行的高帧频成像系统上的自动调光与图像预处理设计方案。通过提升 CMOS 传感器时钟频率、更改高速传输接口(如 CoaXPress 或 CameraLink HS)等方式,获取更优的实时传输性能。若采用较为复杂的加权灰度值作为自动调光反馈信号,能够进一步提升相机对拍摄场景的适应能力。

#### 参考文献:

- [1] 汤雪志 汪志军 ,尹建平 ,等. 弹丸速度测量的高速摄影试验研究 [J]. 兵器装备工程学报 ,2017 ,38(12): 167-170.

- [2] 马帅旗. 基于 FPGA 的高帧频图像跟踪系统设计 [J]. 计算机测量与控制 2019 27(5):169-172 ,177.

- [3] 黄苏南 ,丁圆圆 ,王士龙 ,等. 闭孔泡沫铝动态材料参数的实验研究[J]. 实验力学 2018 33(6):851 -861.

- [4] FUKUDA T ,NAKAGAWA M ,HIROGAKI T ,et al. Investigation of transient response motion of differential planetary gear train during reverse rotation and starting by using high speed camera monitoring [J]. Forschung

- im Ingenieurwesen 2019 83(3):509 520.

- [5] 贾海彦. 基于 FPGA 的高速相机采集系统设计 [D]. 重庆: 重庆理工大学 2016.

- [6] 张龙祥,王向军,曹雨.基于 FPGA 的小型化实时 CMOS 成像处理系统[J]. 电子技术应用 2017 43(5): 78-81 85.

- [7] 辛光泽. 高帧频 CMOS 相机数据存储与显示技术研究 [D]. 西安: 西安工业大学 2014.

- [8] 马林,李锦明,张虎威,等. 高速 CMOS 图像存储与实时显示系统设计[J]. 电子技术应用 2017 43(6):7-10,14.

- [9] SHEN C, YANG W, LIU H, et al. A CMOS high speed imaging system design based on FPGA [C]//AOPC 2015: Image Processing and Analysis. China: SPIE 2015.

- [10] 王洪良. 高速 CMOS 图像传感器的成像控制与传输系统研制[D]. 重庆: 重庆大学 2017.

- [11] 李方宁,王延杰, 涨涛, 等. 基于 AM41V4 传感器的高清高速 CMOS 相机系统设计 [J]. 液晶与显示 2015, 30(3):492-498.

- [12] 刘戚思远 赵德群 邓钱华. 结合自动调光的曝光融合系统设计与实现 [J]. 国外电子测量技术 ,2019 ,38 (9):101-106.

- [13] 张宇,赵贵军,李国宁,等.用于目标跟踪的大视场 CCD 相机自动调光方法及实现[J]. 液晶与显示, 2009 24(6):928-933.

- [14] 申小禾 刘晶红 *楚*广生. 基于直方图分析的航空摄像 机自动调光方法研究 [J]. 电子与信息学报 2016 38 (3):541-548.

- [15] BERNACKI J. Automatic exposure algorithms for digital photography [J]. Multimedia Tools and Applications , 2020 79:12751-12776.

- [16] 焦慧华. 基于 FPGA 的直方图均衡图像增强算法设计及实现[J]. 安徽电子信息职业技术学院学报 2020, 19(5):9-14.

- [17] 温凯. 舰用光电侦察设备多接口光纤传输系统设计 [J]. 光学与光电技术 2020 ,18(4):53 58 ,69.

- [18] 高媛 商远波. 一种基于 CameraLink 的数字图像处理系统[J]. 制导与引信 2017 38(1): 29 32.

- [19] 隋延林 何斌 涨立国 等. 基于 FPGA 的超高速 CameraLink 图像传输 [J]. 吉林大学学报(工学版) 2017, 47(5):1634-1643.

(责任编辑 杨黎丽)